# Utilizing Vera Functional Coverage in the Verification of a Protocol Engine for the FlexRay<sup>TM</sup> Automotive Communication System

Mark Litterick, Verilab

Markus Brenner, Freescale Semiconductor

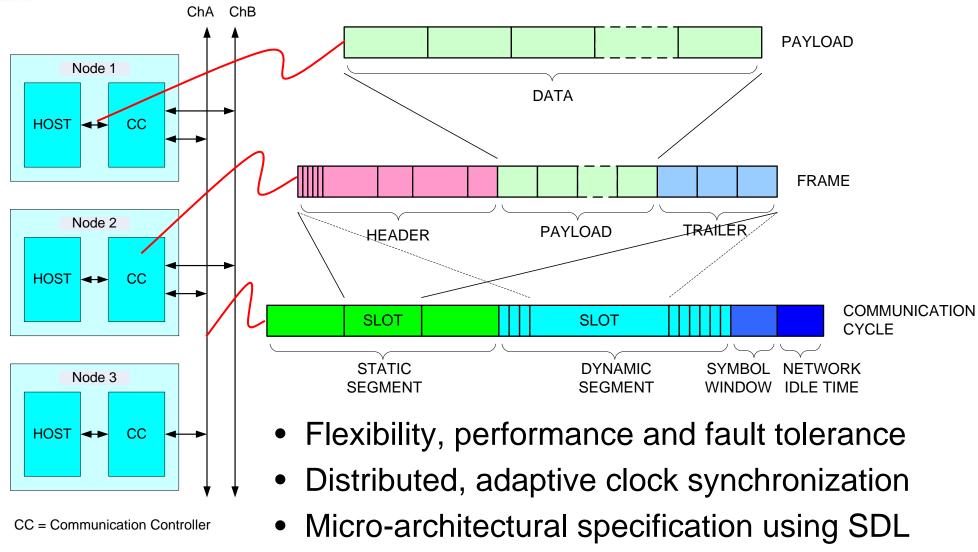

Overview of FlexRay<sup>TM</sup> communications system

- key characteristics

- cluster topology and node architecture

- frame and communication cycle format and hierarchy

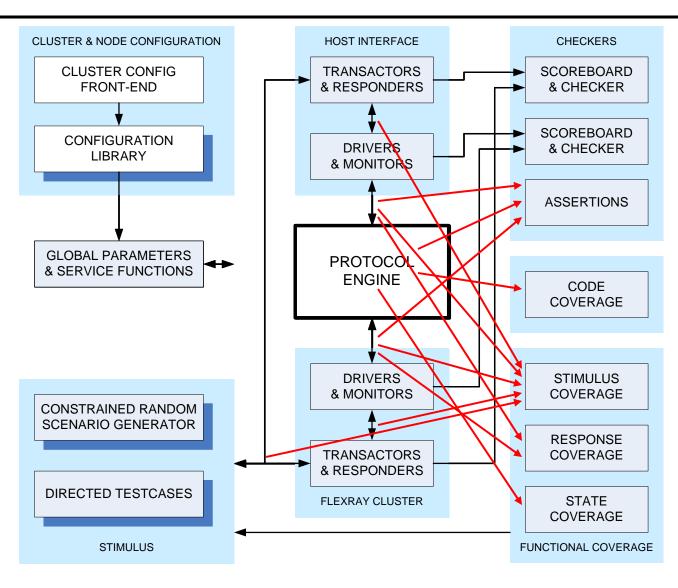

- Testbench architecture

- role of functional coverage

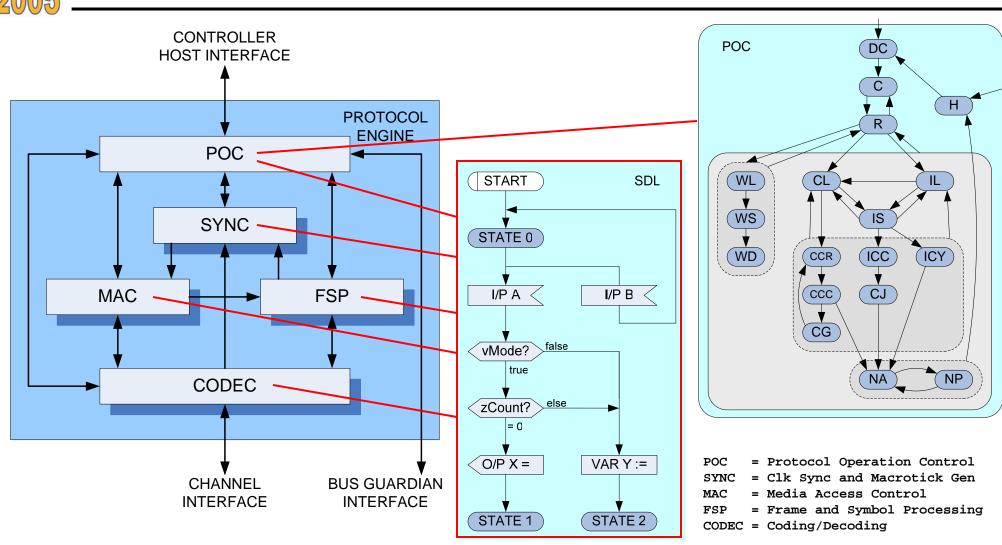

- overview of protocol engine

- Derive internal state coverage for protocol operation controller

- Vera implementation, structure and coding

- Problems and limitations

- Conclusion

# FlexRay<sup>TM</sup> Overview

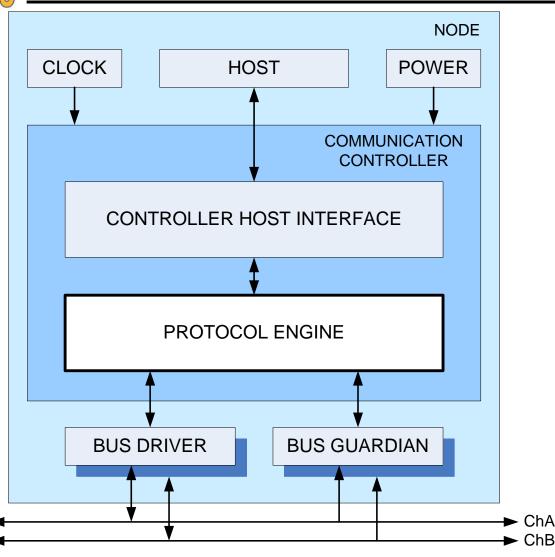

# FlexRay<sup>TM</sup> Node Architecture

- Single or dual channel

- CHI is responsible for registers, data buffers, interrupts, cmds, etc.

- PE provides OSI Layer 2 (Data Link) functionality

- Bus guardian optional

- Typically implemented as single chip (SoC) solution or dual-chip CPU + CC peripheral

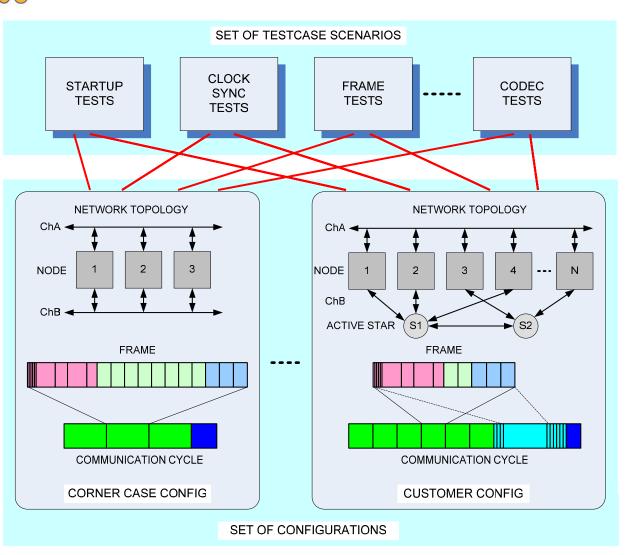

# Protocol Engine Testbench Architecture

# Protocol Engine Architecture

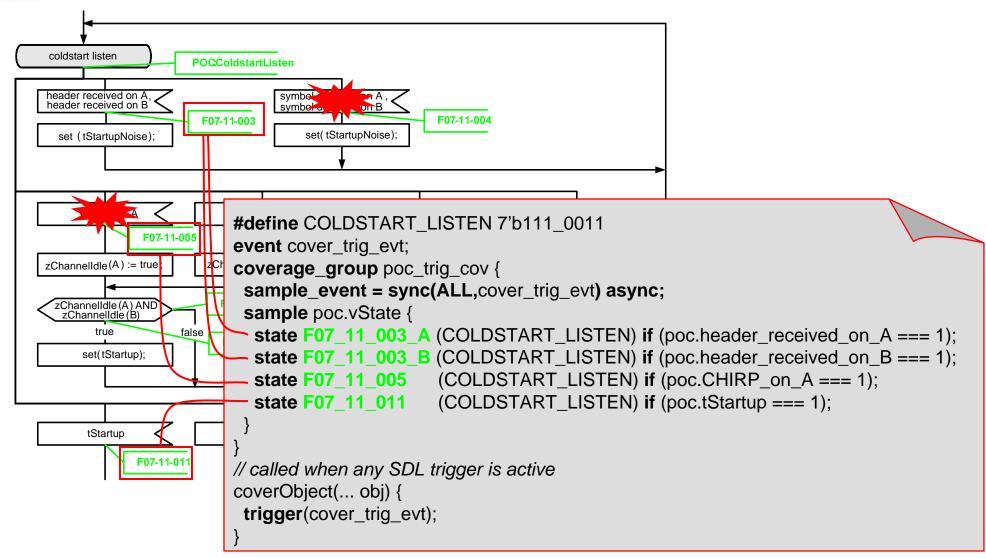

#### Trigger Coverage

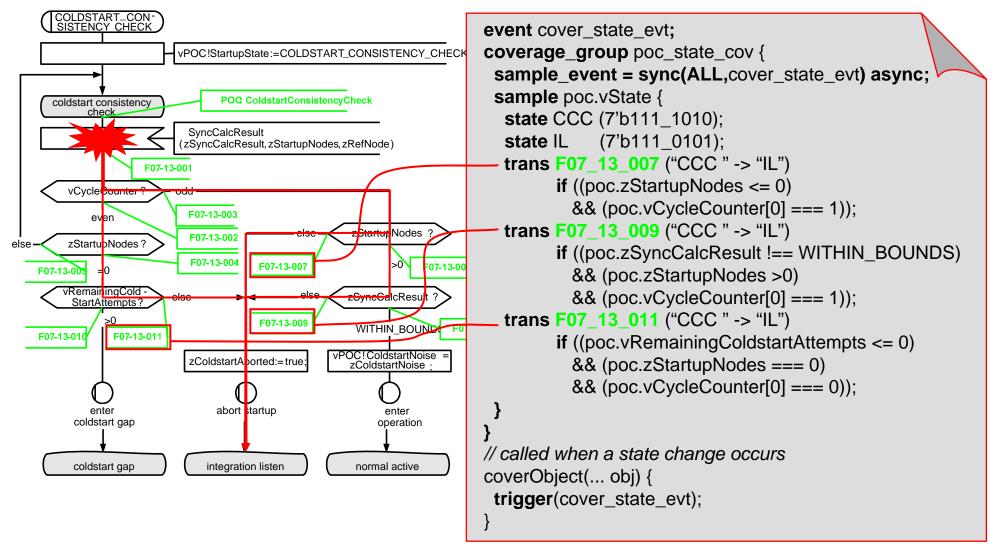

#### State Transition Coverage

#### Vera Implementation

```

task coverObject(...) {

deactivateBin("bin_pattern");

trigger(cover_evt);

// disable bins related to void binds

Coverage Base

DataObjectBase

coverage_group poc_state_cov {

sample event = sync(ALL,cover evt) async;

sample poc.vState {

coverObject()

copy()

wildcard state WL (7'b010_xx01);

queryBin()

equals()

trans DC C ("DC" -> "C");

queryHit()

toString()

trans F02_X ("NP" -> "H") if (poc.a === 1);

deactivateBin()

trans POC1 ("DC" -> "C" -> "NP");

CoverageClass

CoverageMonitor

coverage object

coverage_port

if (change_of_state()) {

coverage object

coverage event

update_poc_obj();

poc_cov.coverObject(poc_obj);

coverage class

coverage_group

CoverageObject

enable()

update_poc_obj() {

disable()

if (vera_is_bound(port.$sig))

queryHit("bin_pattern");

queryHit()

// feedback for constrained random

poc_obj.member = port.$sig;

// checking capability for directed tests

```

#### Managing Coverage Info

- Total coverage

- all tests, all configs

- Config coverage

- all tests, one config

- Test coverage

- one test, all configs

- Achieved through:

- database namespace management

- report merging

- post processing

#### **Problems and Limitations**

- Real-world RTL implementation takes time to calculate & respond

- SDL diagrams are time-independent: many process steps in zero time

- coverage implementation more closely tied to RTL than intended

- Inaccessibility of some variables results in missed coverage

- only a few variables could not be accessed in RTL implementation since stored in RAM (~ 2% coverage)

- Very difficult to reach some protocol corner cases with constrained random stimulus

- many directed tests were required

- Evolution of FlexRay<sup>TM</sup> protocol specification and SDL

- maintenance of spec tags could become an issue

- auto-generation of coverage statements from SDL feasible, but outside the scope of this project

- Pragmatic solution to internal state coverage for Protocol Operation Controller for FlexRay<sup>TM</sup> Communication Controller

- Demonstrated the role of internal state coverage within the overall verification environment

- Functional coverage proved invaluable in measuring effectiveness of constrained-random and directed tests for regression suite

- identifying missing tests and coverage holes

- steering constrained-random tests towards coverage targets

- highlighted testbench infrastructure requirements to enable directed tests

- Vera implementation and code provided are scaleable and usable for a number of similar applications